## Laboratorio di Architetture degli elaboratori (n. 4, 18-19-21/11/02)

1. Realizzare un registro a 3 bit dotato di tre ingressi  $I_2$   $I_1$   $I_0$ , di tre uscite  $A_2$   $A_1$   $A_0$  e di 2 bit  $S_1$   $S_0$  i cui valori selezionano 4 possibili operazioni:

| S <sub>1</sub> | $S_0$ | OPERAZIONE                                |

|----------------|-------|-------------------------------------------|

| 0              | 0     | No change                                 |

| 0              | 1     | Parallel load                             |

| 1              | 0     | Clear A <sub>0</sub>                      |

| 1              | 1     | Clear A <sub>1</sub> and A <sub>0</sub> . |

- 2. Supponendo di rappresentare i numeri interi da 0 a 15 in binario puro, realizzare un circuito a 4 ingressi che determina se l'ingresso rappresenta un numero non divisibile per 3.

- 3. Rifare l'esercizio precedente supponendo che i numeri in ingresso siano compresi tra 0 e 9. Per gli altri valori di ingresso l'uscita non è specificata.

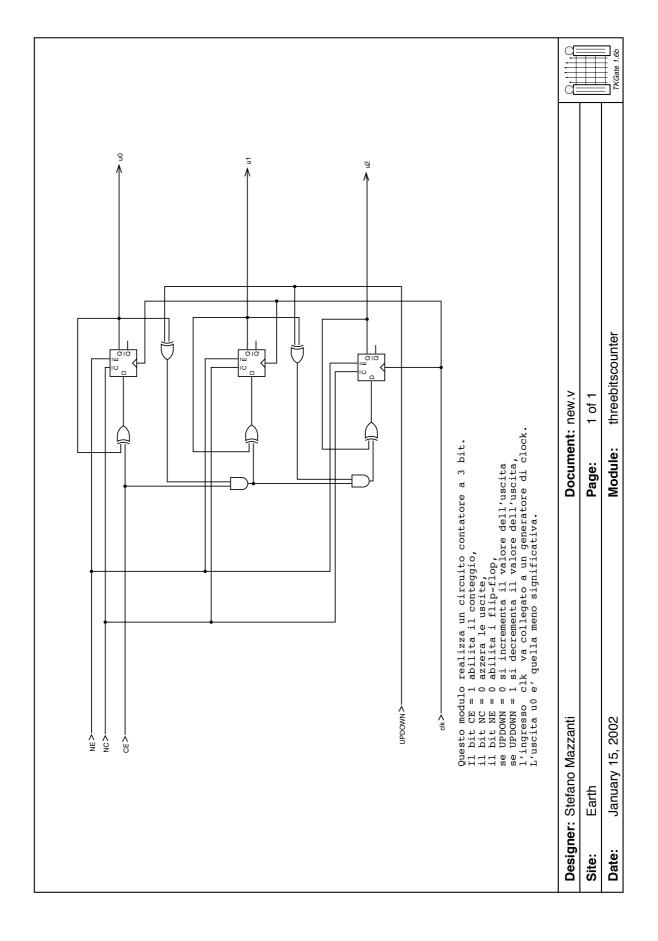

- 4. Realizzare il modulo contatore a 3 bit bidirezionale (up/down) secondo lo schema allegato sul retro.

- 5. Realizzare un secondo modulo contatore che dispone anche di un nuovo ingresso LOAD/COUNT e di tre nuovi ingressi I<sub>2</sub> I<sub>1</sub> I<sub>0</sub>. I flip-flop (e quindi le uscite U<sub>2</sub> U<sub>1</sub> U<sub>0</sub>) devono assumere rispettivamente i valori di I<sub>2</sub> I<sub>1</sub> I<sub>0</sub> quando LOAD/COUNT = 1, altrimenti (LOAD/COUNT = 0) il circuito deve funzionare come il modulo precedente. Si consiglia di modificare il circuito del punto precedente.

- 6. Utilizzando il modulo del punto precedente, realizzare un contatore bidirezionale a 3 bit dotato di due ingressi S<sub>1</sub> S<sub>0</sub> i cui valori selezionano 4 possibili operazioni:

| S <sub>1</sub> | S <sub>0</sub> | OPERAZIONE |

|----------------|----------------|------------|

|                |                |            |

| 0              | 0              | no change  |

| 0              | 1              | up count   |

| 1              | 0              | down count |

| 1              | 1              | reset.     |

7. Simulare il circuito e verificare l'effetto di sincronizzazione del clock sulle uscite del registro (cioè verificare che i valori degli ingressi che determinano i valori di uscita siano quelli che si hanno al momento del fronte di salita/discesa del clock).